## ГОСУДАРСТВЕННЫЙ НАУЧНЫЙ ЦЕНТР РОССИЙСКОЙ ФЕДЕРАЦИИ ИНСТИТУТ ФИЗИКИ ВЫСОКИХ ЭНЕРГИЙ

ИФВЭ 2011– ОЭА

Ю.Д. Карпеков, Ю.С. Киселев, В.А. Сенько

# БЫСТРОДЕЙСТВУЮЩИЕ МНОГОКАНАЛЬНЫЕ МОДУЛИ ВЦП ПИКОСЕКУНДНОГО РАЗРЕШЕНИЯ С ПРОГРАММИРУЕМЫМИ ПАРАМЕТРАМИ

Протвино 2011

УДК 539.1.07 M-24

#### Аннотация

Карпеков Ю.Д., Киселев Ю.С., Сенько В.А.. Быстродействующие многоканальные модули ВЦП пикосекундного разрешения с программируемыми параметрами: Препринт ИФВЭ 2011 – Протвино, 2011. –19 с., 13 рис., 1 табл., библиогр.: 4.

В работе описываются быстродействующие 64 и 128-канальные модули ВЦП пикосекундного разрешения с программируемыми параметрами. Модули разработаны на основе ИС HPTDC1.3 и п.л.и.с. фирмы ALTERA. Модули реализованы в рамках унифицированной в ИФВЭ многоканальной информационной скоростной системы (МИСС) и новой системы электроники ЕвроМИСС.

#### **Abstract**

Karpekov Y.D., Kiselev Y.S., Senko V.A.. A High-Speed multichannels modules TDC of picosecond resolution with programmable parameters: IHEP Preprint 2011 – Protvino, 2011. – p.19, fig.1, tables1, refs.: 4.

The 64 and 128-channel high-speed TDC modules are described. The TDC have programmable parameters and allow to achieve the picosecond resolution. The modules were designed on the base of integrated circuits HPTDC1.3 and ALTERA using FPGA technology. The modules are performed in accordance with demands of high-speed information system MISS and new EvroMISS.

Государственный научный центр Российской Федерации Институт физики высоких энергий, 2011

## Быстродействующие многоканальные модули ВЦП пикосекундного разрешения с программируемыми параметрами

#### Введение

Временные измерения сигналов с пикосекундным разрешением в настоящее время находят все большее применение в различных областях науки и техники. Особая потребность в прецизионных временных измерениях существует при проведении экспериментальных исследований в области физики частиц высоких энергий. Высокая точность измерения времени позволяет получить более точные данные о других параметрах исследуемого процесса. Так, например, в газовых трековых детекторах частиц (дрейфовых камерах) для локализации координаты трека в пространстве с разрешением 50 мкм требуется измерение времени дрейфа носителей электрического заряда с разрешением ~1 нс в широком динамическом диапазоне времени. При идентификации частиц по времени пролета в Time-of-Flight (TOF) детекторах, работающих при больших пучковых загрузках, собственное временное разрешение измерительной аппаратуры должно быть не хуже 25 пс , а разрешение к двум соседним регистрируемым импульсам ~5-10 нс.

Постоянное стремление к увеличению абсолютной и статистической точности временных измерений, а также к повышению эффективности проведения работ на дорогостоящих ускорителях частиц, ведет к широкому развитию систем многоканальных детекторов частиц. Например, современные трековые детекторные системы могут содержать десятки тысяч каналов регистрации [1], сигналы в которых подлежат временным измерениям с пикосекундным разрешением. Поэтому весьма актуальной задачей является разработка многоканальной модульной электронной аппаратуры, предназначенной для высокоточных измерений временных интервалов и представлением результата в цифровой форме. В отечественной технической литературе такая время-измерительная аппаратура получила название Время- Цифровые Преобразователи (ВЦП) или в английской терминологии Time Digital Converter (TDC).

Необходимо также отметить, что многоканальные ВЦП, используемые для временных измерений сигналов с детекторов, работающих в пучках частиц высокой интенсивности, должны обладать повышенным быстродействием, т.е. минимальным мертвым временем между двумя регистрируемыми сигналами, относящимися к разным событиям. Кроме того, при продолжительном времени проведения сеансов физических измерений, многоканальные ВЦП должны обладать долговременной стабильностью характеристик, малым энергопотреблением, повышенной надежностью работы и возможностью легкой адаптации (перепрограммирования параметров) в соответствии с требованиями конкретного физического эксперимента.

Создание эффективных многоканальных модулей ВЦП, отвечающих перечисленным выше требованиям, в сильной степени зависит от наличия на рынке электронных компонентов, а именно быстродействующих интегральных микросхем ВЦП, обладающих предельными значениями технических характеристик для существующего уровня технологии. На момент разработки такими характеристиками обладали зарубежные интегральные микросхемы (ИС) типа HPTDC 1.3 (High Performance Time to Digital Converter) [2], разработанные в электронной группе CERN (Швейцария) для физических экспериментов на ускорителе LHC (Large Hadron Collider) и реализованные в виде специализированных ИС методами заказного проектирования ASIC (Application Specific Integrated Circuit). Эти ИС, выполненные по интегральной технологии 0,25мкм СМОЅ большой степени интеграции (до 106 транзисторов на кристалле), содержат 32 измерительных канала с программируемыми параметрами временного разрешения (800-100 пс/bin.) и мертвого времени в канале (5-100 нс.) в динамическом диапазоне

измеряемого интервала времени  $\sim 51$  мкс . При восьми измерительных каналах HPTDC1.3 способны работать с повышенным временным разрешением (25 пс/bin). Обладая уникальными характеристиками по временному разрешению и быстродействию, HPTDC1.3 имеют более 20-ти программируемых параметров [2].

#### Принцип высокоточного измерения времени в HPTDC1.3

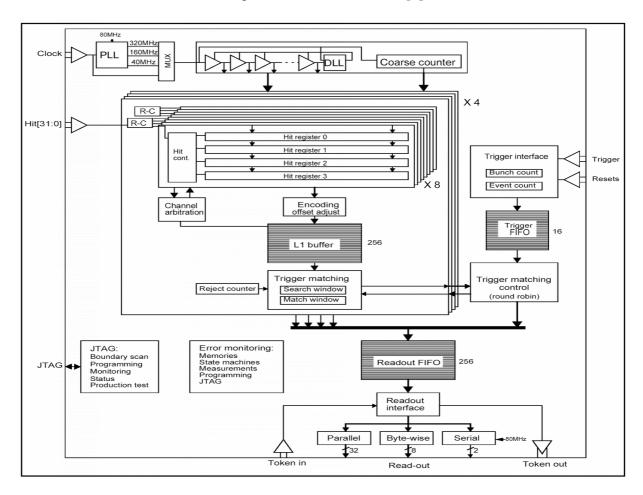

Измерение временных интервалов в HPTDC1.3 (рис.1) осуществляется цифровым способом с использованием интерполяционного метода [4].

Рис.1. Архитектура ИС HPTDC1.3.

При этом методе в дополнение к основному счетчику времени вводится интерполяторустройство, позволяющее уточнить измеряемый временной интервал. Измерение интервалов «грубого» времени в широком динамическом диапазоне времени выполняется с помощью синхронного 15-битного двоичного счетчика **Coarse counter** (рис.1), пересчитывающего импульсы эталонной частоты генератора, заполняющей измеряемый временной интервал. Тактовая частота внутреннего генератора в HPTDC1.3 задается программным способом в диапазоне частот от 40 МГц до 320 МГц. Стабилизация частоты внутреннего генератора обеспечивается с помощью схемы фазовой автоподстройки частоты Phase Locked Loop (**PLL**), которая синхронизируется с частотой внешнего опорного генератора (Clock= 40 МГц).

Измерение «точного» времени в HPTDC1.3 осуществляется схемой интерполятора, выполненного в виде матрицы из 32-х полупроводниковых элементов цифровой задержки с промежуточными отводами (tep n). Для стабилизации параметров элементов задержки они охвачены контуром обратной связи Delay Locked Loop (DLL). Интерполятор дает погрешность, измеряемую долями периода внутреннего генератора. Шаг квантования

интерполятора (bin) вычисляется как T/32, где T —длительность периода тактовой частоты внутреннего генератора. В частности, при максимально возможной тактовой частоте **PLL** -генератора равной 320 МГц ( $T\sim 3$ нс), размер бина интерполятора составляет  $\sim 100$  пс./bin., а измеряемый временной интервал точного времени (**Fine time**) вычисляется как:

Fine time= (tep n)\*100пс, где tep n –номер отвода линии задержки на котором появляется сдвинутый во времени импульс тактовой частоты генератора в момент поступления активного фронта входного **Hit**-сигнала.

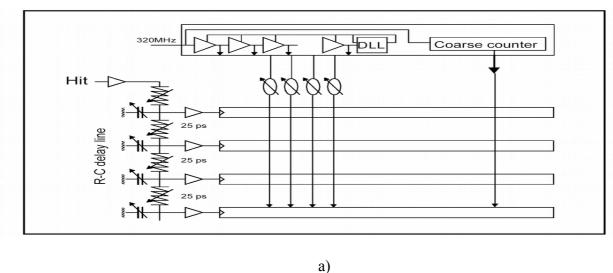

Для получения повышенного временного разрешения при тактовой частоте **PLL** генератора равной 320 МГц, каждые из четырех каналов в ИС HPTDC1.3 объединяются в один измерительный канал, образуя восемь измерительных каналов. При этом в каждом канале входной **Hit**-сигнал поступает на вход аналоговой линии задержки, состоящей из четырех программно регулируемых RC элементов задержки (рис.2, а). В результате каждый 100 пс/bin цифровой задержки на **DLL** разбивается на 4 равных временных интервала по 25пс/bin (рис.2, б).

Рис.2. Повышение временного разрешения HPTDC1.3 при включении между выводами элементов цифровой задержки (tep n) четырех элементов аналоговой задержки на RC-delay line: а) функциональная схема; б) временные диаграммы работы интерполятора.

Как следует из архитектуры HPTDC1.3 (рис.1) каждый измерительный канал содержит четыре быстродействующих входных регистра (**Hit registers**), работающих по принципу FIFO памяти с программируемым разрешением двух соседних **Hit**-сигналов до 5ns. После запоминания **Hit**-сигналов информация о точном времени с выходов **Hit registers** шифруется в 5-битный двоичный код (Fine [4:0]) и вместе со значением двоичного счетчика грубого времени **Coarse counter** (Cnt [14:0]), а также идентификатором номера

сработавшего канала записывается в **L1 buffer** глубиной 256 слов. При этом, формирование двоичного кода полного временного измерения осуществляется путем конкатенации разрядов 5-битного кода на выходе кодировщика точного времени с разрядами 15- битного кода **Coarse counter**, т.е. значения разрядов записываются последовательно друг за другом.

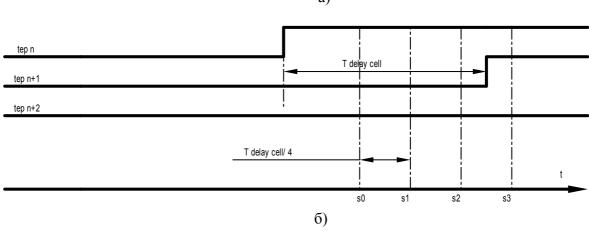

Для сохранения постоянного формата данных во всем динамическом диапазоне измеряемого времени при разных частотах тактового генератора, запись 20- битного кода кодированных данных в L1 buffer, выполняется со сдвигом вправо в соответствии с примерами, иллюстрируемыми на рис.3. В частности, при задании частоты генератора 40MHz (Low resolution) в старшие 12бит L1 buffer записываются отсчеты, соответствующие значению разрядов Cnt [11:0] (разряды Cnt [12:14] игнорируются), а в младшие 8 бит L1 buffer записывается 5-битный код Fine [4:0], соответствующий интерполяционным отсчетам внутри 40 MHz. При выборе частоты генератора 320 MHz (High resolution) в старшие 12бит L1 buffer записываются отсчеты, соответствующие значению разрядов Cnt [14:3], а в младшие 8 бит L1 buffer записывается разряды (Cnt [2:0]) и 5-битный код Fine [4:0]. Как следует из рис.3 при работе HPTDC1.3 с шагом квантования 25 пс. (Very high resolution) при записи кодированных данных в L1 buffer выполняются аналогичные преобразования с добавлением в младшие разряды 2-битного кода интерполяционных отсчетов внутри частоты генератора 320 MHz.

Рис.3. Примеры записи 20-битного кода данных в **L1 buffer** при разных значениях частоты тактового генератора.

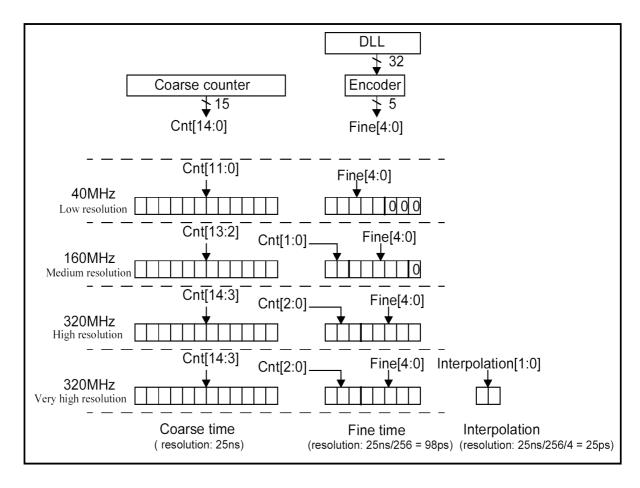

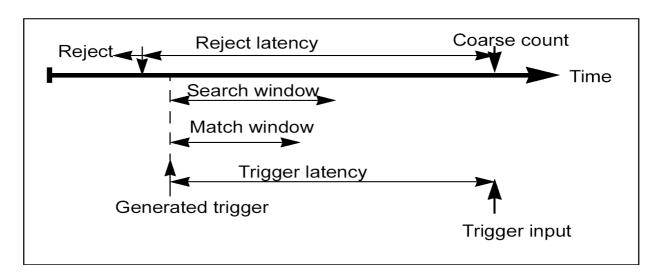

Для запоминания моментов времени генерации триггерных сигналов в HPTDC используется отдельная триггерная FIFO-память глубиной 16 слов. При поступлении на триггерный вход (Trigger input) HPTDC задержанного (Trigger latency) сигнала (рис.4) в триггерную память записывается содержимое **Bunch counter** -временная метка, которая используется для триггерного согласования (trigger matching) с **Hit**-сигналами записанными ранее в **L1 buffer**. После триггерного согласования временная информация из **L1 buffer** записывается в выходной **Readout FIFO** буфер глубиной 256 слов.

Рис.4. Временные соотношения между триггерным сигналом и его задержкой (Trigger latency) внутри программируемого временного «окна» (Match, Search window).

Ниже приводится описание работы быстродействующих многоканальных модулей ВЦП (ЛЭ-84 и ЕМ-3), разработанных на основе ИС НРТОС1.3 Модуль ЛЭ-84 содержит 64 канала регистрации и создан в рамках унифицированной в ИФВЭ многоканальной информационной скоростной системы (МИСС) [3]. Модуль ЕМ-3 содержит 128 каналов регистрации и разработан в рамках новой магистрально- модульной системы электроники ЕвроМИСС. Задание параметров НРТОС1.3 осуществляется в соответствии с требованиями конкретного физического эксперимента с использованием специально разработанных программно-аппаратных средств.

Модули ВЦП предназначены для высокоточных измерений временных интервалов в широком динамическом диапазоне времени при регистрации сигналов в многоканальных детекторах частиц на основе дрейфовых камер, времяпролетных системах на базе резистивных плоских камер (РПК) и других времяизмерительных системах, используемых в физических экспериментах на 70-ГэВ ускорителе ИФВЭ..

#### Структурная схема 64-канального модуля ВЦП ЛЭ-84

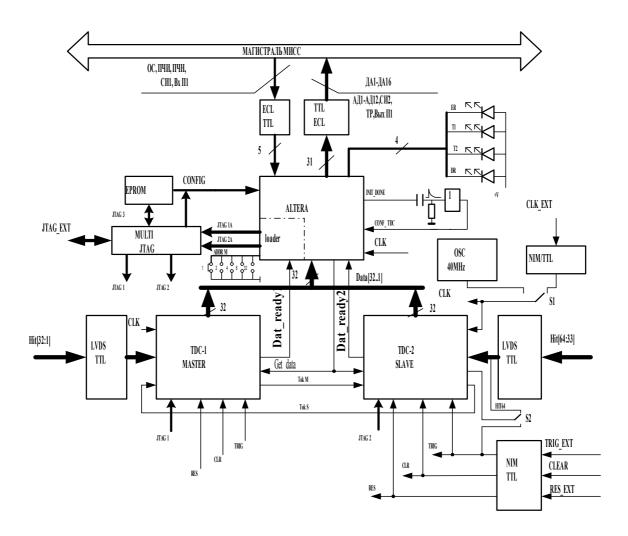

Структурная схема модуля ЛЭ-84 приведена на рис.5. Как уже отмечалось, основу модуля составляют 32-канальные ИС HPTDC 1.3, обозначенные на схеме TDC-1 MASTER и TDC-2 SLAVE, именуемые в дальнейшем просто как TDCi.

Рис.5. Структурная схема модуля ЛЭ-84.

#### Дополнительно в состав модуля входят:

- п.л.и.с. фирмы ALTERA для обмена модуля с магистралью МИСС и аппаратного программирования параметров TDCi;

- EPROM для энергонезависимого хранения конфигурационных данных п.л.и.с. ALTERA;

- Схема MULTI- JTAG для коммутации линий передачи JTAG-сигналов;

- 64 приемника-преобразователя уровней входных сигналов LVDS в уровни TTL TDCi;

- Схемы преобразователей уровней TTL/ECL и ECL/TTL для согласования уровней сигналов п.л.с. ALTERA с уровнями сигналов магистрали МИСС;

• Схема кварцевого автогенератора (OSC 40 MHz) для синхронизации работы TDCi..

#### Режимы работы модуля ЛЭ-84

Работа модуля ЛЭ-84 в рамках системы МИСС осуществляется в трех режимах:

- Инициализации;

- Регистрации;

- ПЧИ.

Режим инициализации модуля ЛЭ-84 выполняется автоматически при включении питания каркаса МИСС. На первом этапе происходит считывание из энергонезависимой памяти EPROM конфигурационных данных проекта в п.л.и.с. ALTERA. При этом в логических блоках п.л.и.с. ALTERA конфигурируется схема интерфейса для обмена TDCi и магистралью МИСС, а также схема loader для аппаратного программирования параметров TDCi. Loader содержит блоки программируемой постоянной памяти LPM JTAG - сигналов. В LPM ROM содержатся JTAG -ROM и узел формирования инструкции и параметры каждого TDCi, записанные в формате mif (Memory Initialization File). После завершения процесса конфигурации п.л.и.с. ALTERA на её выходе генерируется активный уровень сигнала INIT DONE, по переднему фронту которого формируется сигнал CONF\_TDC, осуществляющий запуск схемы loader. В результате работы загрузчика выполняется второй этап инициализации модуля, а именно, аппаратная запись (в соответствие с **JTAG** стандартом IEEE Std 1149.1) рабочих параметров TDCi по двум внутренним портам JTAG1, JTAG2. Окончание режима инициализации модуля ЛЭ-84 индицируется с помощью светодиодов, расположенных на его передней панели.

При отладке режимов работы модуля ЛЭ-84 программирование параметров TDCi и конфигурация п.л.и.с. ALTERA может также выполняться через внешний JTAG\_EXT порт, подключаемый к параллельному LPT порту компьютера с помощью устройства Byte-Blaster. При работе через JTAG\_EXT порт появляется дополнительная возможность программного доступа к встроенной системе тестирования регистров данных и вложенных структур памяти в TDCi. При этом следует отметить, что все регистры в TDCi, входящие в архитектуру системы BST (Boundary Scan Testing), разделены на две группы: установочную (Setup registers) и группу управления (Control registers). После завершения режима инициализации TDCi, во время активной работы модуля ЛЭ-84, содержимое Setup registers не должно изменяться, а содержимое Control registers при необходимости может корректироваться. При работе через JTAG\_EXT порт все необходимые коммутации линий передачи стандартных JTAG- сигналов осуществляются с помощью схемы MULTI- JTAG.

**В режиме регистрации** временные измерения **Hit-** сигналов могут выполняться в трёх программируемых модах:

- С общим триггерным STOP-сигналом;

- В моде парных измерений;

- В бестриггерной моде (режиме накопления).

В зависимости от программно-заданных установок временные измерения могут выполняться в момент поступления активного переднего (leading) или заднего (trailing) фронта **Hit-** сигналов или обоих фронтов leading и trailing. В моде парных измерений возможно измерение длительности **Hit-** сигналов. Начало временного измерения (Т0) **Hit-**сигналов при любой моде работы TDCi имеет временной сдвиг (Offset) относительно положительного фронта сигнала тактовой частоты Clock= 40 МГц опорного генератора. Значение Offset при разном временном разрешении приведено в таблице 1.

Таблица 1.

| TDC mode             | Offset |

|----------------------|--------|

| Low resolution       | 57.5ns |

| Medium resolution    | 23.5ns |

| High resolution      | 11.8ns |

| Very high resolution | 11.1ns |

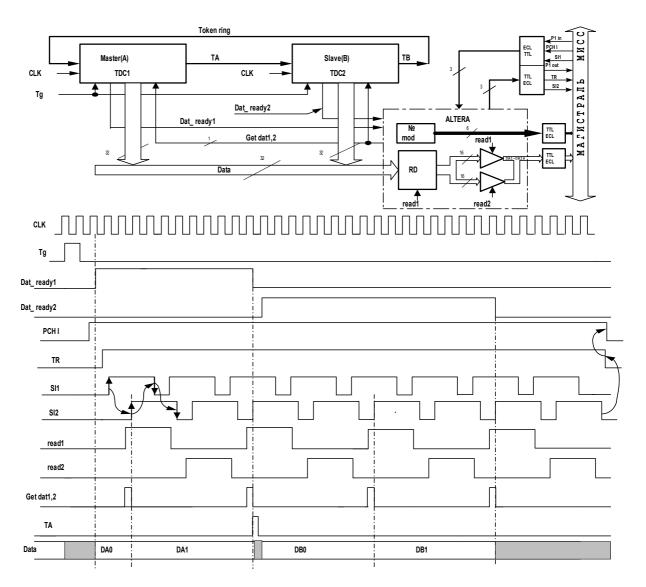

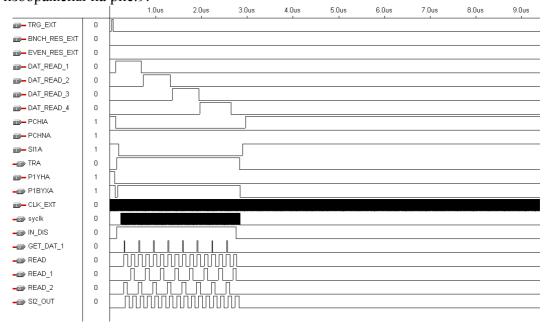

В режиме ПЧИ выполняется операция быстрого чтения кодированных данных из модуля ЛЭ-84 по магистрали МИСС. Инициализация режима ПЧИ осуществляется системным контроллером заданием активного уровня сигнала на магистральной линии ПЧИ. При наличии разрешающего уровня сигнала по последовательной цепи Plin/Plout и активных уровнях сигналов внутренних требований Dat ready1и Dat ready2 модуль устанавливает активный уровень сигнала на магистральную линию TR- требования на его обслуживание. Затем при активном уровне синхросигнала SI1-запроса системного контроллера на чтение данных по магистрали МИСС, происходит считывание через параллельный интерфейс TDCi 32-битного кода кодированных данных в буферный регистр данных RD микросхемы ALTERA. При этом обмен между TDCi и п.л.и.с. ALTERA выполняется в соответствии с протоколом кольцевой сети (Token ring) синхронно с СLК. В свою очередь, чтение 32-битного слова данных из RD на магистраль МИСС осуществляется 16-битными параллельными словами сигналами read1 и read2 за два цикла на магистрали МИСС. Кроме того, в каждом цикле чтения данных модуль выставляет по линиям адреса магистрали МИСС свой адрес (№ модуля) и генерирует ответный синхросигнал SI2, определяющий длительность операции на магистрали МИСС. Операция последовательного чтения завершается при TR=0, т.е. после чтения последнего слова кодированных данных из TDCi. Временные диаграммы работы модуля в режиме ПЧИ изображены на рис.6, а форматы слов кодированных данных, приведены на рис.7.

Рис.6. Временные диаграммы считывания 4-х слов кодированных данных (**DA0-DB1**) из **Readout FIFO** TDCi и их передачи по магистрали МИСС в режиме **ПЧИ**.

**TDC header**: Event header from TDC (master and slaves)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18  | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6    | 5    | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|---|---|----|------|------|---|---|---|---|---|

| 0  | 0  | 1  | 0  |    | TD | C  |    |    |    |    |    | Ev | ent | ID |    |    |    |    |    |    |    |   |   | Bu | ınch | ı ID | ) |   |   |   |   |

TDC: Programmed ID of TDC. Event ID: Event ID from event counter.

Bunch ID: Bunch ID of trigger (trigger time tag).

**TDC trailer**: Event trailer from TDC (master and slaves)

| 3 | 1 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18   | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|---|------|----|----|----|----|----|----|----|----|----|----|----|------|----|----|----|----|----|----|----|----|---|---|---|-----|-----|-----|---|---|---|---|

| ( | 0    | 1  | 1  |    | TD | C  |    |    |    |    |    | Ev | vent | ID |    |    |    |    |    |    |    |   |   | W | ord | cou | ınt |   |   |   |   |

TDC: Programmed ID of TDC. Event ID: Event ID from event counter.

Word count: Number of words from TDC (incl. headers and trailers).

#### **Leading measurement:**

#### Single edge

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21   | 20  | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10   | 9    | 8   | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|------|-----|----|----|----|----|----|----|----|----|----|------|------|-----|----|---|---|---|---|---|---|---|

| 0  | 1  | 0  | 0  |    | TE | C  |    |    | Cl | hanı | nel |    |    |    |    |    |    |    |    | I  | _eac | ling | tin | ne |   |   |   |   |   |   |   |

TDC: Programmed ID of TDC. Channel TDC channel number.

Leading: Leading edge measurement in programmed resolution

Combined measurement of leading and trailing edge (pairing mode)

| 3 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21   | 20  | 19 | 18 | 17 | 16 | 15  | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|---|----|----|----|----|----|----|----|----|----|------|-----|----|----|----|----|-----|-----|----|----|----|----|---|---|---|-----|-----|-----|---|---|---|---|

| 0 | 1  | 0  | 0  |    | TD | C  |    |    | Cl | hani | nel |    |    |    |    | Wio | dth |    |    |    |    |   |   | L | ead | ing | tim | e |   |   |   |

TDC: Programmed ID of TDC. Channel: TDC channel number.

Width: Width of pulse in programmed time resolution.

Leading: Leading edge in programmed time resolution

#### **Trailing measurement:**

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21   | 20  | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|------|-----|----|----|----|----|----|----|----|----|----|----|------|------|-----|---|---|---|---|---|---|---|

| 0  | 1  | 0  | 1  |    | TD | C  |    |    | Cl | hani | nel |    |    |    |    |    |    |    |    |    | Tr | aili | ng t | ime | ; |   |   |   |   |   |   |

TDC: Programmed ID of TDC. Channel TDC channel number.

Trailing: Trailing edge measurement in programmed resolution

Рис.7. Форматы слов кодированных данных, формируемых на выходе **Readout FIFO** TDCi.

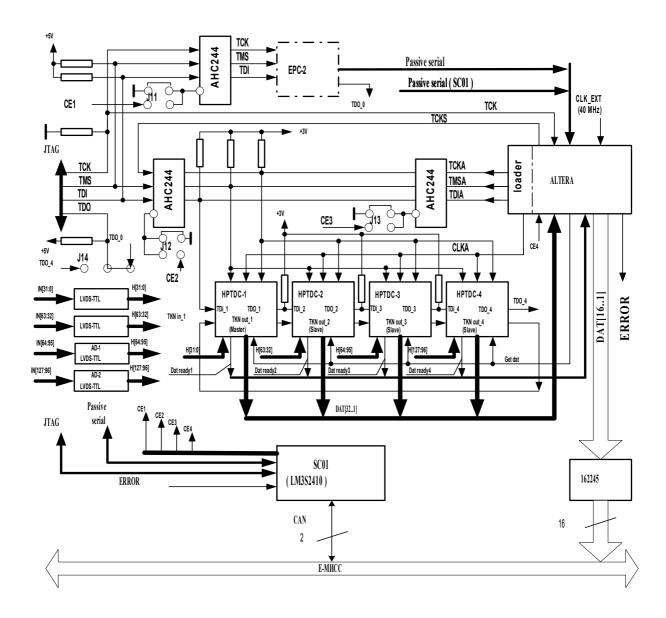

#### Структурная схема 128- канального модуля ВЦП ЕМ-3

Структурная схема модуля ЕМ-3 приведена на рис.8. Основу модуля составляют четыре 32-канальные ИС HPTDC1.3, размещаемые на материнской плате и обозначенные на схеме как HPTDC-1 (MASTER) и HPTDC-2- HPTDC-4 (SLAVE). Кроме того, на материнской плате модуля ЕМ-3 размещаются п.л.и.с. ALTERA, EPROM (EPC-2), а также 64 приемника- преобразователя уровней LVDS входных сигналов IN[63:0] в уровни TTL ИС HPTDCi . Приемники измерительных каналов IN[127:64] располагаются на двух

мезонинных платах **AD-1** и **AD2**, каждая из которых содержит по 32 преобразователя уровней LVDS-TTL. Дополнительно в состав модуля EM-3 входит 32-х разрядный микроконтроллер LM3S2410 фирмы Luminary Micro, размещаемый на мезонинной плате **SC01** и именуемой в дальнейшем как микроконтроллер. Связь микроконтроллера с каркасным контроллером осуществляется через последовательную синхронную шину CAN. Обмен модуля EM-3 с магистралью ЕвроМИСС выполняется с помощью п.л.и.с. ALTERA и 16-канальных микросхем шинных формирователей типа SN74ABT162245D.

Рис. 8. Структурная схема модуля ЕМ-3.

Режимы работы модуля ЕМ-3 аналогичны режимам работы модуля ЛЭ-84. Однако, реализация отдельных режимов в модуле ЕМ-3 имеет принципиальные отличия, которые существенно расширяют функциональные возможности модуля ЕМ-3. Например, в режиме инициализации модуля, конфигурация цепочки из четырёх ИС НРТОСі, осуществляется с помощью встроенного микроконтроллера SC01, что позволяет контролировать и оперативно перепрограммировать параметры ИС НРТОСі непосредственно в ходе проведения физического эксперимента. Кроме того, использование в режиме ПЧИ синхронного протокола обмена с контроллером магистрали ЕвроМИСС, позволило значительно повысить скорость чтения данных из модулей ЕМ-3 в системах сбора данных физических установок ИФВЭ.

#### Режим инициализации модуля EM-3 микроконтроллером SC01

Микроконтроллер SC01 является частью подсистемы медленного контроля магистрально-модульной системы ЕвроМИСС. Кроме мониторинга физических величин (тока, температуры) и тестирования отдельных узлов в электронных модулях, микроконтроллер позволяет выполнять операции конфигурирования как п.л.и.с. ALTERA, так и ИС HPTDCi. Аналогично модулю ЛЭ-84 режим инициализации модуля ЕМ-3 выполняется автоматически при включении питания каркаса ЕвроМИСС. При этом инициализация модуля ЕМ-3 происходит в 2 этапа:

- 1. Загрузка конфигурационной информации из микроконтроллера в п.л.и.с. Altera;

- 2. Загрузка конфигурационной информации из микроконтроллера в ИС НРТОСі. Микроконтроллер хранит конфигурационную информацию во внутренней flash-памяти. В ходе эксперимента конфигурация ИС НРТОСі может быть изменена пользователем через последовательную синхронную шину САN. При этом, пользователю доступны следующие команды:

- Загрузить конфигурационную информацию для ИС HPTDCi из ПК пользователя в RAM микроконтроллера;

- Сохранить конфигурационную информацию ИС HPTDCi из RAM микроконтроллера во flash- памяти.

- Выполнить конфигурацию ИС НРТОСі с общим сбросом;

Для адресации устройств, подключенных к шине CAN, и передачи команды в подсистеме медленного контроля используется стандартный 11-битовый идентификатор кадра CAN, который имеет следующий формат:

| 10 | 9 | 8    | 7 | 6 | 5 | 4 | 3    | 2 | 1 | 0  |

|----|---|------|---|---|---|---|------|---|---|----|

|    |   | TYPE |   |   |   | 1 | ADDF |   |   | BC |

Поле ADDR определяет адрес устройства. Если выставлен бит BC, то посылка является широковещательной (broadcast) и кадр предназначается группе устройств, адрес которых указан в поле ADDR. Если при широковещательной передаче в поле ADDR все биты установлены в состояние "1", то кадр принимают все устройства. Присвоение адреса определенной группе должно происходить каждый раз при инициализации модулей в каркасе ЕвроМИСС.

Поле ТҮРЕ определяет тип передаваемого кадра. Существуют ряд зарезервированных значений этого поля. Оставшиеся свободные значения определяются разработчиком конкретного модуля в системе ЕвроМИСС. Помимо передачи простых команд (записать текущую конфигурацию HPTDCi во flash-память, перезагрузить конфигурацию, предоставить сведения о текущей температуре), существуют команды, требующие передачи данных, как модулю ЕвроМИСС (конфигурация HPTDCi или п.л.и.с. ALTERA), так и от модуля пользователю (показания датчиков в модуле).

Для передачи данных по шине CAN используется соответствующее поле в кадре CAN размером до 8 байт. Если объём данных превышает 8 байт, то передача происходит в несколько этапов. Каждые восемь CAN-кадров приёмник должен квитировать передачу. После передачи 8-ми кадров передатчик ждёт квитирования приёмника. Если ответа не последовало в течении определённого времени, передатчик сбрасывает данную сессию и отправляет сообщение об ошибке приёмнику, после чего передача начинается заново.

Редактирование тех или иных параметров ИС HPTDCi, хранимых во flash-памяти микроконтроллера, выполняется с помощью специально разработанного графического интерфейса, работающего на ПК пользователя под управлением операционных систем общего назначения: Linux, Windows и других. При этом пользователь работает с объемом данных Setup registers только одной ИС HPTDCi, а формирование конфигурационных данных для всей цепочки ИС HPTDCi в микроконтроллере SC01 выполняется программным способом.

#### Работа модуля ЕМ-3 в режиме синхронного ПЧИ

Как уже отмечалось, в режиме ПЧИ в модуле ЕМ-3 реализован синхронный протокол обмена с контроллером магистрали ЕвроМИСС. Инициализация режима ПЧИ осуществляется системным контроллером заданием активного уровня сигнала на магистральной линии ПЧИ. При активных уровнях сигналов внутренних требований Dat ready1- Dat ready4 и разрешающего уровня сигнала на входе последовательной линии P1VHA модуль EM-3 аналогично модулю ЛЭ-84 устанавливает активный уровень сигнала на магистральную линию TR- требования на его обслуживание. Затем, при активном уровне синхросигнала SI1-запроса системного контроллера на чтение данных по магистрали ЕвроМИСС происходит считывание синхронно с CLK и в соответствии с протоколом Token ring 32-битных кодированных данных из Readout FIFO TDCi в буферный регистр RD п.л.и.с. ALTERA. Чтение данных из RD на магистраль ЕвроМИСС происходит за два цикла сигналами READ 1, READ 2. При этом время выполнения одной операции на магистрали ЕвроМИСС зависит от частоты следования синхросигналов SI2 OUT, генерируемых модулем ЕМ-3. После чтения последнего слова кодированных данных из последнего ТDCi, режим синхронного ПЧИ завершается установкой модулем EM-3 сигнала TR=0,. Временные диаграммы работы модуля EM-3 в режиме синхронного ПЧИ изображены на рис.9.

Рис.9. Временные диаграммы считывания 8-и слов кодированных данных из **Readout FIFO** TDCi и их передачи по магистрали E-МИСС в режиме синхронного **ПЧИ**.

## Тестовые измерения временного разрешения модулей ЛЭ-84 и EM3

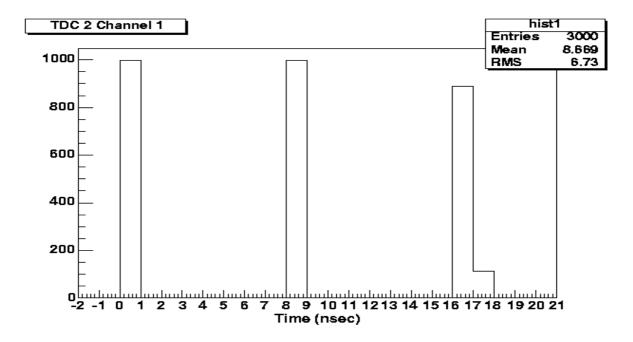

Тестирование разработанных модулей ВЦП на соответствие программно-заданного временного разрешения ИС HPTDC1.3 проводилось при низком (шаг квантования 781nc/bin) и высоком (шаг квантования 98nc/bin) разрешении с использованием разных методов измерения. Например, тестирование модулей при низком временном разрешении осуществлялось традиционным методом, при котором измерялось время прохождения переднего фронта (leading-Edge) тестового сигнала через отрезки коаксиального кабеля с известной величиной погонной задержки. Применение коаксиального кабеля для формирования калибрационных временных сдвигов обеспечивало высокую стабильность задаваемых временных интервалов и минимальное искажение формы тестового сигнала. В процессе измерений тестовый сигнал длительностью  $\tau = 40$  нс., сформированный в стандарте NIM, подавался на один из измерительных входов тестируемого модуля и одновременно на вход коаксиального кабеля с волновым сопротивлением  $\rho$ = 50 Ом. Далее, задержанный тестовый сигнал с выхода кабеля поступал на соседний измерительный вход. Для согласование однофазного тестового NIM- сигнала с парафазными уровнями LVDS-сигналов на входах измерительных каналов использовался специальный модуль трансляции уровней NIM-LVDS.

В ходе испытаний набиралась статистика при трех значениях кабельной задержки, коммутируемой с шагом 8нс. Преобразованные в ТDCi данные считывались в режиме ПЧИ по магистрали сектора МИСС и накапливались в памяти ЭВМ. Затем файлы, содержащие данные временных отсчетов для 3000 событий, обрабатывались в ЭВМ системой гистограммирования ROOT. При этом измеряемые интервалы времени вычислялись путем вычитания из отсчетов, регистрируемых в канале после линии задержки, значений отсчетов в канале перед линией задержки. Гистограммы измеренных интервалов времени при шаге квантования 781 пс/bin представлены на рис.10. При этом точность измерения (RMS) фиксированных интервалов времени составила ~ 0,45 bin (351пс).

Рис.10. Распределение измеренных интервалов времени при трех фиксированных значениях кабельной задержки тестового сигнала при шаге квантования 781 пс/bin.

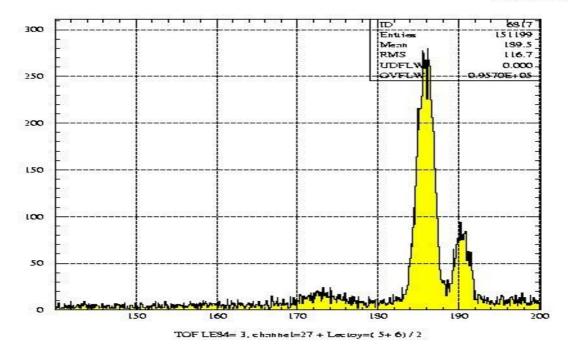

Тестирование модулей при шаге квантования 98пс/bin осуществлялось реальными, изменяющимися во времени сигналами, регистрируемыми на выходе ФЭУ сцинтилляционного ТОГ детектора, работающего на пучке частиц ускорителя У-70 ИФВЭ. При тестировании модулей измерялось время пролета заряженных частиц, обладающих одинаковым импульсом. В ходе испытаний аналогичные временные измерения проводились с помощью модуля ТDС 2228A фирмы LeCroy с шагом квантования 50 пс/bin Сравнительный анализ результатов временных измерений, полученных с использованием модуля TDC 2228A и разработанных модулей ВЦП показал их хорошее согласие в пределах заданной погрешности измерений.

На рис.11 представлены спектры времени пролета положительных частиц с импульсом 2 ГэВ/с на базе 15м. в ТОГ детекторе установки СПИН., измеренные с помощью модуля ЛЭ-84 на пучке частиц ускорителя У-70 ИФВЭ. Первый пик справа (шкала времени в нс. идет справа налево) - это пионы, затем протоны и последний широкий- это дейтроны. Интервалы времени между пиками временного спектра хорошо согласуются с расчетными временами пролета частиц.

2008/12/23 13.10

Рис.11. Спектры времени пролета положительных частиц в ТОF детекторе установки СПИН, измеренные модулем ЛЭ-84 при шаге квантования 98 ps/bin.

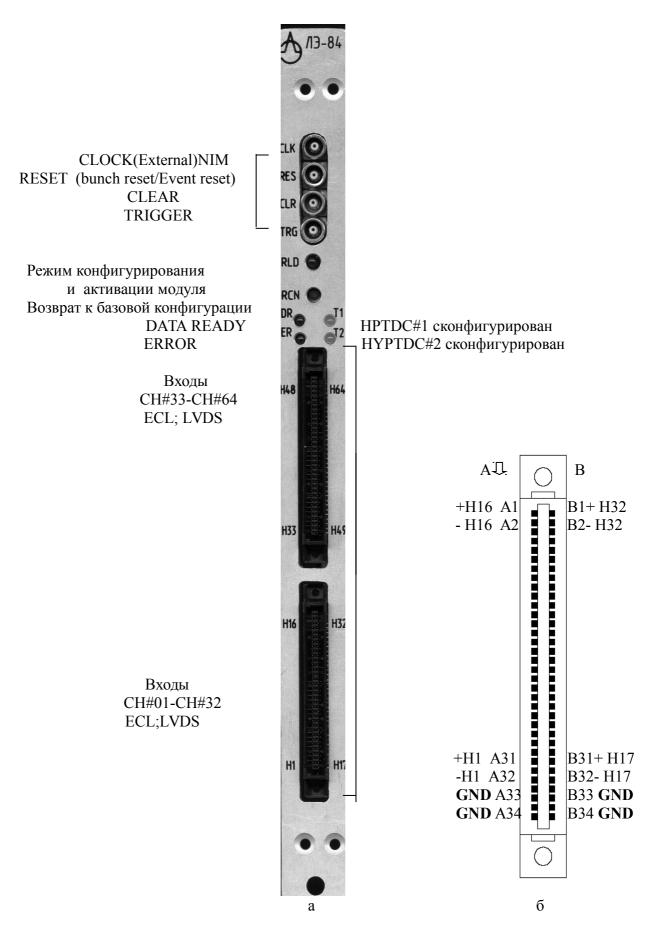

#### Конструктивное исполнение модулей ЛЭ-84 и ЕМ-3

Как отмечалось ранее модули ВЦП разработаны в разных механических и электрических стандартах. Модуль ЛЭ-84 выполнен в виде блока единичной ширины в стандарте МИСС. На передней панели модуля (рис.12а) расположены два многоконтактных разъема типа P50E-068P1-SR1-EA для приема входных сигналов (Н1-Н64). Назначение контактов одного из сигнальных разъемов показано на рис.12б. На передней панели модуля также размещаются четыре коаксиальных разъема для приема сигналов управления «CLK», «RES», «CLR», «TRG». Уровни входных сигналов – парафазные ECL или LVDS. Уровни сигналов управления соответствуют стандарту NIM. Дополнительно на передней панели модуля расположены светодиодные индикаторы, «DR», «ER», «T1», «T2» назначение которых отражено на рис. 12.

Рис.12. Лицевая панель (а) и входной сигнальный разъём (б) модуля ЛЭ-84. +H – положительный активный уровень входного сигнала

-Н – отрицательный активный уровень входного сигнала

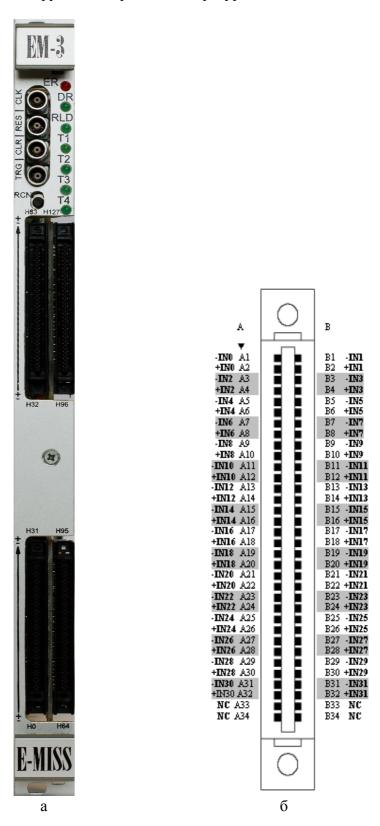

Модуль ЕМ-3 выполнен в виде блока единичной ширины высотой 6U и глубиной 280 мм в стандарте Евромеханики (рис.13). Как отмечалось выше модуль содержит материнскую плату и три мезонинные платы: АД1,АД2 и SC01. На передней панели модуля расположены четыре многоконтактных разъёма типа P50E-068P1-SR1-EA для приема входных сигналов (H0-H127) и четыре коаксиальных разъёма для управляющих сигналов, назначение которых аналогичны модулю ЛЭ-84. Светодиодные индикаторы Т1 - Т4 индицируют о завершение конфигурации HPTDC-1 - HPTDC-4.

Рис.13. Лицевая панель (а) и входной сигнальный разъём (б) модуля ЕМ-3.

#### Заключение

На основе разработанных модулей ЛЭ-84 создана многоканальная аппаратура на 1280 каналов регистрации для временных измерений сигналов в дрейфовых камерах установки ОКА ИФВЭ. С использованием модулей ЛЭ-84 создана также аппаратура на 640 каналов регистрации для измерения длительности сигналов в РПК детекторах на установке СПИН ИФВЭ. На базе модулей ЕМ-3 создаётся время-измерительная аппаратура на 6500 каналов регистра для дрейфовых камер новой установки СПАСЧАРМ ИФВЭ. Опыт эксплуатации разработанной аппаратуры на экспериментальных установках ИФВЭ показал стабильность её характеристик и достаточную надежность в работе.

В заключение авторы выражают благодарность А.В. Сидорову за участие на начальном этапе разработки, Н.А. Кузьмину за помощь в обработке и анализе результатов временных измерений при лабораторных испытаниях модуля ЛЭ-84. Глубокую признательность авторы выражают также Ю.М. Свиридову и В.И. Романовскому за помощь при проведении тестовых измерений временных характеристик модулей на пучке частиц 70-Гэв ускорителя ИФВЭ.

#### Список литературы

- [1] ATLAS Muons detector.

- [2] J. Christiansen HPTDC Version 1.3, CERN/EP-MIC

- [3] Бушнин Ю.Б. и др. Быстродействующая система регистрирующей и триггерной электроники для экспериментальных исследований в ИФВЭ. Препринт ИФВЭ 88-47. Серпухов, 1988.

- [4] Мелешко Е.А. Наносекундная электроника в экспериментальной физике. М.Энергоатомиздат,1987.С 139.